بخشی از پاورپوینت

--- پاورپوینت شامل تصاویر میباشد ----

اسلاید 1 :

انتساب پیوسته رویه ای

برای قرار دادن مقدار یک عبارت به صورت پیوسته و غالب در یک متغیر به کار می رود.

نتیجه این انتساب نسبت به انتساب رویه ای غالب است.

در فرایند تست و عیب یابی کاربرد دارد.

اسلاید 2 :

این انتساب به دو روش پیاده سازی می گردد:

- با کلمات کلیدی assign و deassign

- با کلمات کلیدی force و release

اسلاید 3 :

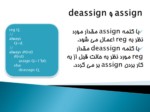

assign و deassign

سمت راست حتماً reg و یا ترکیبی از reg ها است.

سمت چپ نمی تواند آرایه ای از reg ها باشد.

درون بلوک های رفتاری استفاده می شوند.

اسلاید 4 :

با کلمه assign مقدار مورد نظر به reg اعمال می شود.

با کلمه deassign مقدار reg مورد نظر به حالت قبل از به کار بردن assign بر می گردد.

اسلاید 5 :

force و release

سمت چپ می تواند متغیری از نوع reg و یا net باشد.

درون بلوک های رفتاری استفاده می شوند.

اسلاید 6 :

با کلمه force مقدار مورد نظر به متغیر اعمال می شود.

با کلمه release مقدار متغیر مورد نظر به حالت قبل از به کار بردن force بر می گردد.

اسلاید 7 :

جایگزینی پارامترها

در Verilog می توان مقادیر پارامتر ها را هنگام ترجمه عوض کرد.

این کار با استفاده از کلمه کلیدی defparam و یا هنگام فراخوانی ماژول صورت می گیرد.

اسلاید 8 :

defparam

مقدار پارامتر های هر ماژول را (با ذکر سلسله مراتب) می تواند تغییر دهد.

درون ساختار خود ماژول استفاده می شود.

برای آدرس دهی پارامترها، ساختار سلسله مراتبی به کار می رود.

اسلاید 9 :

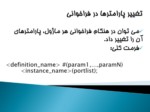

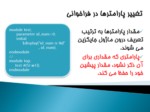

تغییر پارامترها در فراخوانی

می توان در هنگام فراخوانی هر ماژول، پارامترهای آن را تغییر داد.

فرمت کلی:

<definition_name> #(param1,…,paramN) <instance_name>(portlist);

اسلاید 10 :

مقدار پارامترها به ترتیب تعریف درون ماژول جایگزین می شوند.

پارامتری که مقداری برای آن ذکر نشود، مقدار پیشین خود را حفظ می کند.