بخشی از پاورپوینت

--- پاورپوینت شامل تصاویر میباشد ----

اسلاید 1 :

Outline

- FIR filter on ADPS-21x

DSP Requirements

- Fast Multiply-Accumulates (Data-path)

- Extended Precision Accumulator Register (Data-path)

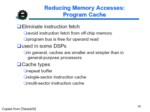

- Dual Operand Fetch (Memory)

- Circular Buffering (Addressing)

- Zero-Overhead Looping (Instruction set)

Analog Devices Architectures and Programming

- SHARC

- Blackfin

- Performance Optimization

اسلاید 2 :

FIR filter steps

- Obtain a sample with the ADC; generate an interrupt

- Detect and manage the interrupt

- Move the sample into the input signal's circular buffer

- Update the pointer for the input signal's circular buffer

- Zero the accumulator

- Control the loop through each of the coefficients

- Fetch the coefficient from the coefficient's circular buffer

- Update the pointer for the coefficient's circular buffer

- Fetch the sample from the input signal's circular buffer

- Update the pointer for the input signal's circular buffer

- Multiply the coefficient by the sample

- Add the product to the accumulator

- Move the output sample (accumulator) to a holding buffer

- Move the output sample from the holding buffer to the DAC

اسلاید 3 :

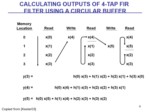

FIR filter steps (cont.)

ADSP21xx Example code:

CNTR = N-1;

DO convolution UNTIL CE;

convolution:

MR = MR + MX0 * MY0(SS), MX0 = DM(I0,M1), MY0 = PM(I4,M5);

اسلاید 4 :

- FIR filter on ADPS-21x

DSP Requirements

- Fast Multiply-Accumulates (Data-path)

- Extended Precision Accumulator Register (Data-path)

- Dual Operand Fetch (Memory)

- Circular Buffering (Addressing)

- Zero-Overhead Looping (Instruction set)

Analog Devices Architectures and Programming

- SHARC

- Blackfin

- Performance Optimization

اسلاید 5 :

- FIR filter on ADPS-21x

DSP Requirements

- Fast Multiply-Accumulates (Data-path)

- Extended Precision Accumulator Register (Data-path)

- Dual Operand Fetch (Memory)

- Circular Buffering (Addressing)

- Zero-Overhead Looping (Instruction set)

Analog Devices Architectures and Programming

- SHARC

- Blackfin

- Performance Optimization

اسلاید 6 :

- FIR filter on ADPS-21x

DSP Requirements

- Fast Multiply-Accumulates (Data-path)

- Extended Precision Accumulator Register (Data-path)

- Dual Operand Fetch (Memory)

- Circular Buffering (Addressing)

- Zero-Overhead Looping (Instruction set)

Analog Devices Architectures and Programming

- SHARC

- Blackfin

- Performance Optimization

اسلاید 7 :

- Software loop:

MOVE #16,B Initialize loop counter B

LOOP: MAC (R0)+,(R4)+,A Register-indirect addressing with post-increment

DEC B

JNE LOOP

- Hardware loops: no time is spent on

–Decrementing counters

–Checking to see if the loop is finished

–Branching back to the top of the loop

RPT #16

MAC (R0)+,(R4)+,A

اسلاید 8 :

- FIR filter on ADPS-21x

DSP Requirements

- Fast Multiply-Accumulates (Data-path)

- Extended Precision Accumulator Register (Data-path)

- Dual Operand Fetch (Memory)

- Circular Buffering (Addressing)

- Zero-Overhead Looping (Instruction set)

Analog Devices Architectures and Programming

- SHARC

- Blackfin

- Performance Optimization

اسلاید 9 :

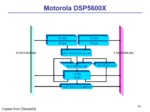

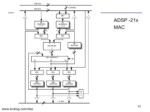

- The Super Harvard ARChitecture

- 100MHz Core / 300 MFLOPS Peak

- Parallel Operation of: Multiplier, ALU, 2 Address Generators &

Sequencer

–No Arithmetic Pipeline; All Computations Are Single-Cycle

- High Precision and Extended Dynamic Range

–32/40-Bit IEEE Floating-Point Math

–32-Bit Fixed-Point MAC’s with 64-Bit Product & 80-Bit Accumulation

- Single-Cycle Transfers with Dual-Ported Memory Structures

–Supported by Cache Memory and Enhanced HarvardArchitecture

- Glueless Multiprocessing Features

- JTAG Test and Emulation Port

- DMA Controller, Serial Ports, Link Ports, External Bus, SDRAM

Controller, Timers

اسلاید 10 :

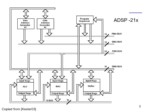

ADSP-2106x Core Architecture