بخشی از پاورپوینت

--- پاورپوینت شامل تصاویر میباشد ----

اسلاید 1 :

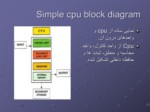

Clock : با شارش CLK wire، سی پی یو یک دستور را اجرا می کند و(clock cycle) به تعداد دستورهایی که سی پی یو در دوره می تواند انجام دهد clock speed گفته می شود.

MCC:تراشه کنترل کننده حافظه که نامهای مختلف دیگری نیز دارد.

Pipelining : به نوعی توسعه clock، هر محل کاری cpu کار خود را با یکclock pulse انجام می دهد. به طور واقعی اجرای هر دستور را قبل از خاتمه اجرای دستور قبلی شروع می نماید.

Stage :Fetch،Decode ، Execute، Write

Thread: هر برنامه ای به تعدادی قسمت های کوچکی شکسته می شود. این نخها برای کارهای ویژه ای طراحی شده اند.

اسلاید 2 :

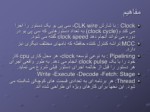

hyperthreading : نوعی توسعه واحد اجرایی در cpuهای اینتل که به نظر سیستم عامل دو هسته ای است.

MCH: توسعه MCC توسط اینتل

Crossbar switch:((AMD آدرسها را جمع آوری کرده و توزیع می کند و داده را از هر هسته به هسته دیگر یا باقی سیستم توزیع می کند. در خواست های هسته ها را برای داده ها بهتر برآورد می کند.

HyperTransport Link or Bus :(Opteron (AMDاین به چیپ های دوهسته ای امکان می دهد که از داخل خودcpu با یکدیگر با سرعتی بیش از 6GB/s ارتباط برقرار کنند. یک خط مستقیم برای ارتباط با دیگر دستگاههای PC با سرعت بالا و حذف ایده FSB، MCC و تکنولوژی Double-pumped و قرار دادن MC در cpu .

اسلاید 3 :

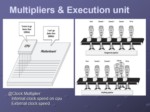

: (multimedia extensions) MMXاولین ایده برای پردازش گرافیک در Pentium.

3Dnow!: فناوری AMD در K6 برای رقابت با MMX

Streaming SIMD Extensions) SSE):

فناوری Intel در Pentium ||| برای رقابت با 3Dnow!.

اسلاید 4 :

@Back side bus: cpu & cache

@Double-pumped FSB: Double the data rate with out increasing the clock speed. double the data transfers per clock cycle on speed of bus). First in Athlon Thunderbird.

Quad-pumped: Intel made

@Integer unit / Floating point unit

@I-cache / D-cache

اسلاید 5 :

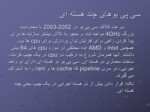

سرعت کلاک سی پی یو در 2002-2003 با محدودیت بزرگ 4GHz مواجه شد، و منجر به تلاش بیشتر سازنده ها برای پیدا کردن راهی برای افزایش توان پردازش برای cpu ها بود. همچنین Intel و AMD ایده مختلفی در مورد cpu های 64 بیتی داشتند. آنها همزمان شروع به ترکیب دو cpu در یک چیپ کردند، ساخت معماری دو هسته ای. سی پی یو دو هسته ای دارای دو واحد اجرایی، دو سری pipeline که cacheها و ram را به اشتراک می گیرند.

نکته: قرار دادن بیش از دو هسته اجرایی در یک چیپ یعنی چند هسته ای.

اسلاید 6 :

اینتل با تولید Pentium D با دو نسل آخر Pentium 4 اولین سی پی یو دو هسته ای را وارد بازار کرد. هر هسته دارای cache خود بود و Frontside bus را به اشتراک گرفته بودند. و دارای لیسانس AMD64 معروف به سی پی یو های “Smarts” inside که قادر به اجرای کدهای 32 و 64 بیتی است. اینتل نام این را EM64T گذاشت.

اسلاید 7 :

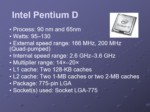

- Watts: 89–110

- Physical address: 40 bits

- External speed range: 200 MHz (System clock)

- Internal speed range: 2.0 (3800+)–2.4 (4000+) GHz

- Multiplier range: 10×–12×

- L1 cache: 128 KB

- L2 cache: Two 512-KB caches or two 1-MB caches

- Package: micro-PGA

- Socket(s) used: Socket 939, Socket AM2

اسلاید 8 :

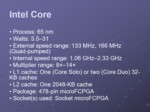

طی چند سال اخیر پردازنده های رومیزی Intel در وضعیت مناسبی قرار نداشته اند. CPUهای Pentium 4 و Pentium D با سرعت Clock نسبتاً بالایی کار می کنند اما در مقایسه با رقیب خود یعنی AMD عملکرد ضعیفتری داشته اند. همچنین برق بسیار زیادی مصرف می کنند که بیشتر آن به صورت گرما تلف می شود. به عبارت دیگر داغتر و کندتر بوده اند. علی رغم تلاش های انجام شده توسط مهندسین Intel و انواع تولید، این تراشه ها بر اساس ریز معماری افزایش شبکه (Net burst) قادر نبوده اند بخوبی بر محدودیت های ذاتی شان غلبه کنند تا با Athlon 64 برابری نمایند. در نتیجه Intel تصمیم گرفت Net burst را کنار بگذارد و روی طرح جدید کارآمد و کم مصرف مربوط به طرح تیم اسرائیلی که مسئول Pentium M بود، کار کند.

اینتل در سال 2006 پایان Pentium را با معرفی Intel Core اعلام کرد. و شروع به تولید اولین نسل پردازشگرهای core بر پایه Pentium M کرد. بیشتر به سبک معماریPentium Pro بود.تک هسته ای (solo) و دو هسته ای (Duo) نام گرفت که هر دو 478 پین بودند.

اسلاید 9 :

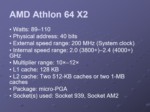

- Process: 65 nm

- Watts: 5.5–31

- External speed range: 133 MHz, 166 MHz (Quad-pumped)

- Internal speed range: 1.06 GHz–2.33 GHz

- Multiplier range: 8×–14×

- L1 cache: One (Core Solo) or two (Core Duo) 32-KB caches

- L2 cache: One 2048-KB cache

- Package: 478-pin microFCPGA

- Socket(s) used: Socket microFCPGA

اسلاید 10 :

معماری جدید هسته

اضافه شدن درستورالعمل sse4

استفاده از تکنولوژی 65 نانو

دو برابر شدن کش L1

سریعتر شدن سرعت کش

مصرف پایین

استفاده از فناوری 32 نانو در آینده نزدیک