بخشی از پاورپوینت

--- پاورپوینت شامل تصاویر میباشد ----

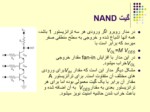

اسلاید 1 :

مقدمه

lمنطق TTL با استفاده از ترانزیستورهای دو قطبی ساخته میشود که به عنوان سوئیچ اشباع عمل میکنند.

lتاخیر ناشی از خارج کردن سوئیچ از حالت اشباع یک عامل مهم در محدود کردن سرعت این منطق است که البته روشهائی برای غلبه بر آن ارائه شده است.

lامروزه مدارات Schottky TTL بصورت گسترده ای در کاربردهائی که نیاز به ارتباط با سرعت بالا با مدارات بیرونی دارند نظیر مادربرد ها بکار میروند.

اسلاید 2 :

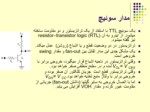

مدار سوئیچ

lیک سوئیچ TTL با استفاد از یک ترانزیستور و دو مقاومت ساخته میشود. از اینرو به آن resistor–transistor logic (RTL) نیز گفته میشود.

lترانزیستور در دو وضعیت قطع و یا اشباع (روشن) عمل میکند.

lیک مشکل جدی این مدار تقابل بین fan-out و مقدار swing خروجی است.

lوقتی ترانزیستور در ناحیه اشباع قرار میگیرد، خروجی برابر با VOL= V CES شده و در سطح منطقی صفر خواهد بود.

lوقتی ترانزیستور قطع است جریان کلکتور آن صفر بوده و خروجی برابر با ولتاژ منبع تغذیه خواهد بود. VOH= V CC

lاما با اتصال خروجی به سایر گیتها (داشتن fan-out) جریانی از مقاومت عبور کرده و مقدار VOH افزایش می یابد.

اسلاید 3 :

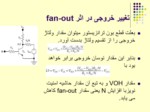

تغییر خروجی در اثر fan-out

lاگر خروجی یک گیت RTL به تعدادی گیت( که برای سادگی مشابه فرض میشوند) وصل شود در اثر جریان کشیدن این گیتها مقدار خروجی تحت تاثیر قرار میگیرد.

lبرای محاسبه اثر گیت های بار میتوان آنها را با معادل تونن خود جایگزین نمود.

اسلاید 4 :

تغییر خروجی در اثر fan-out

lبعلت قطع بون ترانزیستور میتوان مقدار ولتاژ خروجی را از تقسیم ولتاژ بدست آورد.

lبنابر این مقدار نوسان خروجی برابر خواهد بود با

lمقدار VOH و به تبع آن مقدار حاشیه امنیت نویزبا افزایش N یعنی مقدار fan-out کاهش می یابد.

اسلاید 5 :

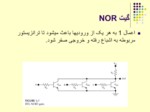

گیت NOR

lاعمال 1 به هر یک از ورودیها باعث میشود تا ترانزیستور مربوطه به اشباع رفته و خروجی صفر شود.

اسلاید 6 :

lدر مدار روبرو اگر ورودی هر سه ترانزیستور 1 باشد، همه آنها اشباع شده و خروجی به سطح منطقی صفر میرسد که برابر است با

lVOL=M VCES

lدر این مدار با افزایش fan-in مقدار خروجی VOLخراب میشود.

lمشکل دیگر مدار این است که مقدار VIHبرای ورودی های مختلف آن متفاوت است. برای ترانزیستور A مقدار آن برابر با یک گیت معمولی بوده اما برای هر ترانزیستور بعدی به مقدار VCES به آن اضافه شده و باعث خراب شدن حاشیه امنیت نویز میشود.

اسلاید 7 :

منطق DTL

lمنطق RTL از مشکل swing و نویز رنج میبرد. برای حل این مشکلات منطق DTL معرفی گردید.

lوجود دیود باعث میشود تا در صورت یک بودن خروجی جریانی از خروجی گیت کشیده نشود. لذا مشکل تغییر swing در اثر fan-out از بین میرود. در مدار زیر مشکل اختلاف ورودیها در اثر fan-in نیز از بین رفته است.

اسلاید 8 :

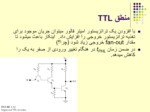

l با اعمال تغییراتی در منطق DTL منطق دیگری با نام TTL بوجود آمد که در آن دیود های موجود در ورودی با ترانزیستور جایگزین گشته اند. برای اینکار دو دیود پشت به پشت با هم ادغام و به صورت یک ترانزیستور npn ساخته شدند. در این مدار ناحیه p دیودها با هم ادغام شده و ضمن صرفه جوئی در جا، خازن پارازیتی کمتر و در نتیجه تاخیر انتشار کمتری نیز دارد.

lعلاوه برآن بدلیل اینکه ترانزیستور ورودی در هنگام انتقال ورودی از یک به صفر بصورت فعال در می آید، باعث میشود تا بار موجود در بیس ترانزیستور خروجی به سرعت تخلیه شود. که در نهایت سرعت مدار را افزایش میدهد.

اسلاید 9 :

lبا افزودن یک ترانزیستور امیتر فالور میتوان جریان موجود برای تغذیه ترانزیستور خروجی را افزایش داد. اینکار باعث میشود تا مقدار fan-out خروجی زیاد شود (چرا؟)

lدر ضمن زمان tPHL در هنگام تغییر ورودی از صفر به یک را کاهش میدهد.

اسلاید 10 :

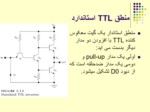

منطق TTL استاندارد

lمنطق استاندار یک گیت معکوس کننده TTL با افزودن دو مدار دیگر بدست می اید:

lاولی یک مدار pull-up و دومی یک مدار ضدحلقه است که از دیود D0 تشکیل میشود.